### HaRTES project

# Hard Real-Time Ethernet Switching

# **Project overview**

Paulo Pedreiras

Kickoff meeting, April 17, 2009, Aveiro

### Background

#### Initial work on Ethernet networks at the LSE:

- Started in 2001

- FTT-Ethernet

- shared Ethernet

- FTT-SE

- switched Ethernet

- VTPE

- implicit token passing, "PNet like" protocol

### Background

Some issues common to all COTS implementations have been identified:

- Necessarily cooperative

- All nodes have to comply with the protocol

- Complex handling and signalization mechanism for aperiodic traffic

- Scalability and efficiency problems for this class of traffic

- Impossible to implement traffic policing

- Serious fault-tolerance problems

Those limitations can be addressed by using a **custom switch**, which led to the proposal of the HaRTES project

- Initially proposed in 2005, European project, with several partners

- University of Aveiro, Balearic Islands University, ZHW, Austrian Academy of Sciences, Czech Technical Univ. in Prague, Catania University

- Good evaluation but ... not good enough!

- In 2006 submitted to the Portuguese FCT Foundation (slim version)

- Good evaluation but ... not good enough again! After complaining ... we got luck!

HaRTES project - kickoff meeting

General objective:

Develop FPGA-based switching technology for Ethernet, capable of providing real-time communication services with operational flexibility.

Specific objectives:

1. To include transmission control capabilities in Ethernet switches allowing the synchronization of parallel flows in different ports and the triggering of transmissions with low jitter;

### Specific objectives (cont):

- 2. Integrate flexible scheduling and QoS management services inside an Ethernet switch with transmission control capabilities:

- Real-time communication objects can be added, removed or updated on-line, with timeliness guarantees.

- 3.Traffic management features to **separate different traffic classes** at the input ports and handle them with **mutual isolation**.

- Seamless integration of ordinary Ethernet nodes (e.g. PCs) with general-purpose operating systems without jeopardizing the real-time properties. HaRTES project - kickoff meeting

April 17,2009

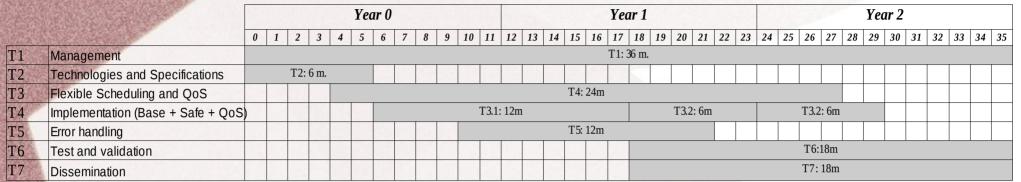

#### Task schedule

#### Resources

#### Manpower

- Faculty staff:

- Luís Almeida

- Paulo Pedreiras

- Arnaldo Oliveira

- Valter Filipe Silva

- Joaquim Ferreira

- Post-grad

- Ricardo Marau (PhD)

- Rui Santos (PhD)

- Ricardo Moreira (Msc)

- José Alberto Fonseca

Grants (27month)

- Alexandre Vieira

#### Budget

Total of 90K Euros

#### Project organization:

- T1 Management

- Global project management issues

- Results

- Successful execution of the project, according to the respective plan.

- All the necessary progress and final reports

- **Coordination** of project activities and interaction between team members.

### T2 Technologies and specifications

Survey of relevant switch technologies and architectures & evaluation of resource requirement due to the enhanced features (e.g. CPU, memory)

#### - Results

- Identification and characterization of relevant switching technologies and architectures

- Technical specifications of the enhanced switches to be developed within the project

- Assessment of the impact of the enhanced features of the prototype switches in terms of functionality and requirements.

### T3 Flexible scheduling and QoS

Research on flexible scheduling & QoS management algorithms suitable to HW implementation. Specification of a middleware for accessing the extended services.

#### - Results

- Development of on-line scheduling mechanisms and algorithms

- Specification and development of QoS management policies suitable for on-line application.

- Definition of an adequate **middleware** to access the flexible scheduling and QoS management related services.

#### T4 Implementation

- Implementation of prototype switches.

Broken down in 3 sub-tasks, each dedicated to building one switch with increasing functionality levels:

- (B)**Basic**: extends a standard Ethernet switch with traffic sched. & transm. control capab.

- (S) **Safe**: extends the Basic switch with traffic policing capabilities.

- (Q) **QoS**: extends the Safe switch with dynamic QoS features.

#### - Results:

Three operational prototype switches (B,S,Q)

### T5 Error handling

Error detection and containment issues (main focus on the time domain). Detection of error nature (permanent vs transient), avoid error propagation, disconnection and reintegration of nodes, ...)

#### Results

- Fault model for the S and Q switches;

- Specification and development of error detection mechanisms;

- Specification and development of faulttreatment mechanisms (port isolation and reintegration mechanisms).

#### T6 Test and validation

Design & development of a test suit required to verify the capabilities of the proposed switches. Validation of the switches and their dependability analysis, using adequate modeling tools.

#### Results

- **Test set** for each of the switches to verify and validate each of their specific features.

- Results of the execution of the test sets.

- Validated switches (concerning their specifications).

### T7 Dissemination

Project promotion and results dissemination (fliers, website and special sessions in industrial/scientific events). Development of a demonstrator (distributed control system) using the HaRTES switches.

#### - Results

- Publicity materials, website, organization of seminars and special sessions in related events, both scientific and industry-oriented.

- Demonstrator using the prototype switches in a setup that includes video streaming, feedback control, dynamic QoS management and unconstrained NRTtraffooject - kickoff meeting

### Current status (1)

#### Two PhD students involved in the last two years

- Definition of the switch architecture

- Basic switch functionality achieved:

- Traffic dispatching and confinement

- Prospective work / new services & functionality

- Server-based switch for managing asynchronous traffic (already validated in FTT-SE)

- Flexible cycle organization, full asynchronous mode

### Current status (2)

Threats:

- Initial objectives proposed nearly 4 years ago

- Lack of resources to carry out the work at the proper pace!

- ... we are not alone anymore!!!

- Main competitors: Profinet & TTP/Ethernet

- Inflexible management of RT traffic

- Statically scheduled, run-time changes not allowed or severely limited and inefficient;

- Poor or no support of soft real-time traffic;

- Lack of support for dynamic QoS manag.

- ... so the HaRTES goals are still relevant