Fábio Miguel Nogueira Implementação de pilha protocolar tempo-real para Amado vídeo industrial

# Amado

# Fábio Miguel Nogueira Implementação de pilha protocolar tempo-real para vídeo industrial

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia Electrónica e Telecomunicações, realizada sob a orientação científica do Professor Doutor Paulo Pedreiras, Professor Auxiliar do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro.

Apoio financeiro da FCT por via do projecto HaRTES - Comutação Tempo-Real, Ethernet de com referência PTDC/EEA-ACR/73307/2006.

Dedico este trabalho aos meus pais, à minha namorada, à minha família,

ao meu avô...

### o júri

presidente

# Prof. Doutor José Alberto Gouveia Fonseca

Professor Associado do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro

vogais

Prof. Doutor Paulo José Lopes Machado Portugal Professor Auxiliar do Departamento de Engenharia Electrotécnica e de Computadores da Faculdade de Engenharia da Universidade do Porto

#### Prof. Doutor Paulo Bacelar Reis Pedreiras (Orientador)

Professor Auxiliar do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro

#### agradecimentos

Gostaria de agradecer às seguintes pessoas no âmbito pessoal:

Aos meus pais, que sempre acreditaram em mim, sempre me apoiaram, sempre me motivaram, e me deram condições para ser o que sou hoje. O meu muito obrigado!

À minha namorada, Mariana da Vitória Costa, que me mudou como pessoa, me tornou um ser mais humano, sociável e ouvinte. Sem esquecer que é a minha alma gémea que me completa. Obrigado amor!

A toda a minha família, pelo apoio, amor e carinho dados e pela quota-parte de responsabilidade na minha educação.

A todos os meus amigos que ao longo dos tempos coloriram a minha vida. Quem me conhece sabe bem o valor que dou à amizade. Não serão esquecidos!

"Feliz daquele que encontra um amigo digno desse nome" Menandro

À Associação de Defesa Pessoal, na pessoa do Professor Vítor Gomes, que contribuiu activamente para me melhorar como pessoa, dia-a-dia, um pouco de cada vez.

A todos os bons professores que tive a felicidade de encontrar; mais importante do que saberem transmitir o conteúdo programático, souberam incutir o gosto pelo conhecimento, pelo estudo. Sem vocês provavelmente não teria chegado onde cheguei.

No âmbito pessoal e académico que a esta dissertação diz respeito, gostaria de agradecer:

Ao professor Paulo Pedreiras, por me ter acompanhado sempre de uma forma atenta, pela motivação incutida, e pelo conhecimento técnico irrepreensível. Agradeço ainda pelo bom ambiente criado entre orientador e orientando.

Ao Sr. Carlos Breda e Sra. Rosário Breda, por terem apostado em mim, e me terem facilitado a conclusão deste meu processo de formação. Obrigado também pelas palavras amigas e de apoio dadas em momentos de indecisão, demonstrando sempre total disponibilidade e abertura.

Ao meu colega e amigo Nuno Marujo, por me ter ajudado na revisão desta dissertação e ter contribuído com alguns conselhos para a elaboração da mesma.

À empresa Riamolde - Engenharia e Sistemas S.A. por ter emprestado algum do *hardware* utilizado no âmbito desta dissertação.

A todos os meus colegas que ao longo do meu percurso académico de alguma forma contribuíram para a minha formação.

#### palavras-chave

Ethernet, FTT-Ethernet, FTT-SE, Industrial Ethernet, tempo-real, controlo, controlo distribuído, sistemas distribuídos, comunicações industriais

#### resumo

Actualmente as necessidades de sistemas de tempo-real estão presentes em muitos campos da nossa sociedade. Desde um simples sistema de vídeo-conferência até à automação de uma fábrica.

A tendência destes últimos anos é a de uniformizar meios de transmissão de informação tendo em vista a redução de custos.

A rede *Ethernet* está bastante disseminada em vários sectores, sejam eles fabris, domésticos, telecomunicações, etc.

No entanto, esta não consegue fornecer garantias de tempo-real dado aos seus mecanismos indeterminísticos de acesso ao meio. Existem várias soluções desenvolvidas por diversos fabricantes para tentar colmatar estas limitações inerentes ao protocolo.

Esta dissertação utiliza uma dessas soluções de Industrial Ethernet: o protocolo FTT-SE (*Flexible Time Trigger over Switched Ethernet*), na implementação de uma *stack* tempo-real para uma câmara de vídeo industrial. Adicionalmente são apresentados alguns resultados e conclusões da implementação.

#### keywords

Ethernet, FTT-Ethernet, FTT-SE, Industrial Ethernet, real-time, control, distributed control, distributed systems, industrial communications

#### abstract

Nowadays real-time systems are present in several fields of our society. From a simple video conference system to factory automation.

The trend of recent years is to standardize the means of transmitting information with the purpose of cost reduction.

The Ethernet network is widely disseminated in various sectors, whether manufacturing, domestic, telecommunications, etc.

However, it cannot deliver real-time guarantees given to its indeterministic mechanisms for medium access.

There are several solutions developed by different manufacturers to help overcome these limitations inherent to the protocol.

This dissertation uses one of these solutions for Industrial Ethernet: the FTT-SE protocol (Flexible Time Trigger over Switched Ethernet), on the implementation of a real-time stack for an industrial video camera. Additionally, some results and conclusions of the implementation are presented.

# Conteúdo

| I | Enq  | uadramento e motivação                                            | 1  |

|---|------|-------------------------------------------------------------------|----|

|   | 1.1  | Descrição da dissertação                                          | 1  |

|   | 1.1. | 1 Trabalho anterior                                               | 2  |

|   | 1.1. | 2 Objectivos                                                      | 2  |

|   | 1.2  | Estrutura da Dissertação                                          | 3  |

| 2 | Con  | ceitos Fundamentais                                               | 5  |

|   | 2.1  | Definição de sistema                                              | 5  |

|   | 2.2  | Definição de sistema de controlo                                  | 5  |

|   | 2.3  | Evolução do controlo digital                                      | 5  |

|   | 2.4  | Sistema de Tempo-Real                                             | 6  |

|   | 2.4. | 1 Significado                                                     | 6  |

|   | 2.4. | 2 Tipos de sistemas de tempo-real                                 | 7  |

|   | 2.4. | Classificação do tipo de mensagens em relação à sua periodicidade | 8  |

|   | 2.5  | Características de um sistema de tempo-real                       | 8  |

|   | 2.6  | Sistemas de controlo centralizado versus distribuído              | 9  |

| 3 | A re | ede Ethernet                                                      | 11 |

|   | 3.1  | Breve descrição do protocolo                                      | 11 |

|   | 3.2  | Protocolos <i>Ethernet</i> existentes com garantias de tempo-real | 13 |

|   | 3.   | 2.1.1 PROFINET                                                    | 13 |

|   | 3.   | 2.1.2 ETHERNET POWERLINK                                          | 14 |

|   | 3.   | 2.1.3 TTETHERNET                                                  | 15 |

| 4 | Flex | cible Time Trigger (FTT)                                          | 19 |

|   | 4.1  | Introdução                                                        | 19 |

|   | 4.2  | Breve resumo do paradigma FTT                                     | 19 |

|   | 4.2. | 1 Arquitectura base                                               | 19 |

|   | 4.2. | 2 Funcionalidades                                                 | 20 |

|   | 4.3  | Flexible Time Trigger over Switched Ethernet (FTT-SE)             | 21 |

|   | 4.3. | 1 Trama FTT-SE                                                    | 21 |

|   | 4.   | 3.1.1 Tipos de mensagens                                          | 21 |

|   | 4.   | 3.1.2 Trigger Message                                             | 22 |

|   | 4.   | 3.1.3 Synchronous Data Message – SDM                              | 23 |

|   | 4.   | 3.1.4 Asynchronous Data Message – ADM                             | 24 |

|   | 4.   | 3.1.5 Asynchronous Signalling Message – ASM                       | 24 |

| 4.3.   | .2 Elementary cycle do protocolo FTT-SE                                  | 25                 |

|--------|--------------------------------------------------------------------------|--------------------|

| 4.4    | Variantes do paradigma FTT                                               | 26                 |

| 5 Sist | tema desenvolvido                                                        | 27                 |

| 5.1    | Ambiente de desenvolvimento                                              | 27                 |

| 5.2    | Breve descrição do hardware                                              | 28                 |

| 5.2.   | .1 Placa de desenvolvimento                                              | 28                 |

| 5.2.   | .2 Placa de expansão <i>Ethernet</i>                                     | 29                 |

| 5.2.   | .3 Emulador                                                              | 29                 |

| 5.2.   | .4 Computadores utilizados                                               | 30                 |

| 5.3    | Software existente                                                       | 30                 |

| 5.3.   | .1 Código exemplo                                                        | 30                 |

| 5.3.   | .2 Master simulado                                                       | 31                 |

| 5.4    | Software desenvolvido                                                    | 32                 |

| 5.4.   | .1 Inicializações                                                        | 32                 |

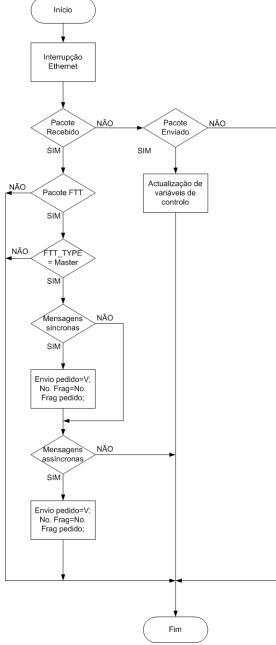

| 5.4.   | .2 Rotina de atendimento a eventos <i>Ethernet</i>                       | 32                 |

| 5.4.   | .3 Acções para o envio de uma trama Ethernet                             | 34                 |

| 5.4.   | .4 Acções para a recepção de uma trama <i>Ethernet</i>                   | 35                 |

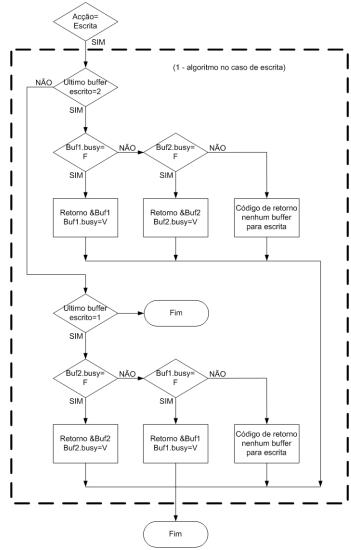

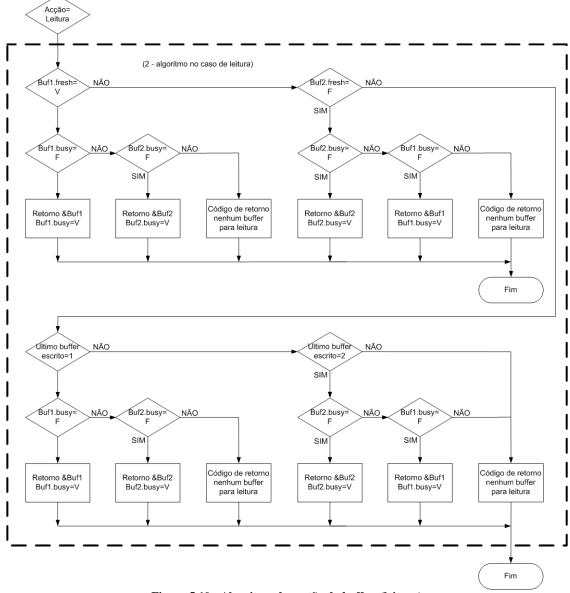

| 5.4.   | .5 Mecanismo de troca de <i>buffers</i>                                  | 36                 |

| 5.5    | Descrição dos testes                                                     | 38                 |

| 5.5.   | .1 Experiência 1: Tempo de resposta                                      | 39                 |

| 5.     | 5.5.1.1 Master                                                           | 39                 |

| 5.     | 5.5.1.2 Slave                                                            | 40                 |

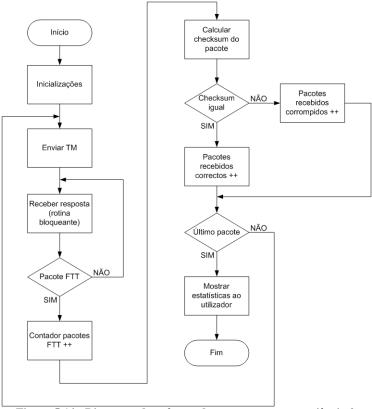

| 5.5.   | .2 Experiência 2: Integridade dos dados                                  | 41                 |

| 5.     | 5.5.2.1 Master                                                           | 42                 |

| 5.     | 5.5.2.2 Slave                                                            | 43                 |

| 5.5.   | .3 Experiência 3: Fragmentação e reagrupamento                           | 44                 |

| 5.     | 5.5.3.1 Master                                                           | 44                 |

| 5.     | 5.5.3.2 Slave                                                            | 45                 |

| 5.5.   | .4 Experiência 4: Mecanismo duplo <i>buffer</i>                          | 46                 |

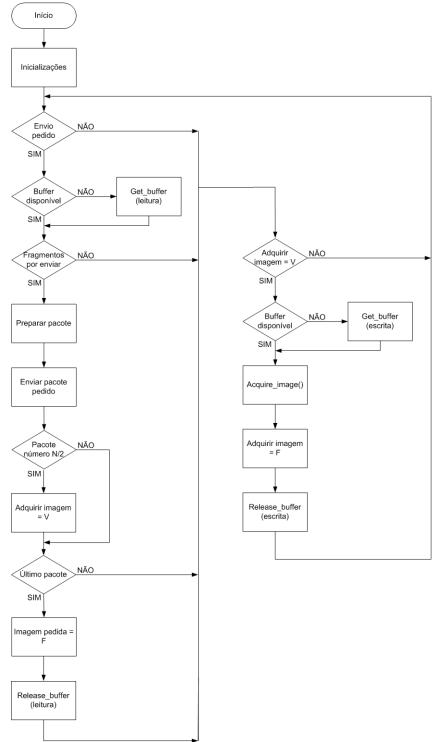

| 5.     | 5.5.4.1 Master                                                           | 48                 |

| 5.     | 5.5.4.2 Slave                                                            | 49                 |

| 5.5.   | .5 Experiência 5: Mecanismo de troca de <i>buffers</i> com interferência | em N/250           |

| 5.     | 5.5.5.1 Master                                                           | 50                 |

| 5.     | 5.5.5.2 Slave                                                            | 50                 |

| 5.5.   | .6 Experiência 6: Mecanismo de troca de <i>buffers</i> com interferência | de <i>timer</i> 52 |

| 5      | 5.5.6.1 Master                                                           | 55                 |

|   | 5   | .5.6.2 Slave                                                            | 55 |

|---|-----|-------------------------------------------------------------------------|----|

| 6 | Res | sultados experimentais                                                  | 57 |

| 6 | .1  | Experiência 1: Tempo de resposta                                        | 57 |

| 6 | .2  | Experiência 2: Integridade dos dados                                    | 58 |

| 6 | .3  | Experiência 3: Fragmentação e reagrupamento                             | 58 |

| 6 | .4  | Experiência 4: Mecanismo duplo buffer                                   | 59 |

| 6 | .5  | Experiência 5: Mecanismo de troca de buffers com interferência em N/2   | 60 |

| 6 | .6  | Experiência 6: Mecanismo de troca de buffers com interferência de timer | 60 |

| 7 | Co  | nclusões                                                                | 63 |

| 7 | .1  | Análise de resultados                                                   | 63 |

| 7 | .2  | Análise de objectivos                                                   | 63 |

| 7 | .3  | Trabalho Futuro                                                         | 63 |

# Lista de figuras

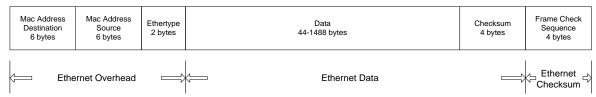

| Figura 3.1 - Formato da trama <i>Ethernet</i>                                        | 12 |

|--------------------------------------------------------------------------------------|----|

| Figura 3.2 – Modularidade do protocolo PROFINET                                      |    |

| Figura 3.3 - Exemplo de um ciclo POWERLINK                                           |    |

| Figura 3.4 - Os três tipos de tráfego TTEthernet                                     | 16 |

| Figura 3.5 - Rede TTEthernet com bus guardians redundantes                           | 17 |

| Figura 4.1 – Arquitectura base do paradigma FTT                                      |    |

| Figura 4.2 - Ciclo elementar do paradigma FTT                                        |    |

| Figura 4.3 - Trama FTT-SE                                                            |    |

| Figura 4.4 - Estrutura de uma <i>trigger message</i>                                 | 22 |

| Figura 4.5 – Campos introduzidos por cada mensagem síncrona de dados                 |    |

| Figura 4.6 - Campos introduzidos por cada mensagem assíncrona de dados               | 23 |

| Figura 4.7 – Exemplo genérico de uma trigger message                                 |    |

| Figura 4.8 - Exemplo específico da formação de uma trigger message                   |    |

| Figura 4.9 - Estrutura de uma mensagem de dados síncrona                             |    |

| Figura 4.10 – Estrutura de uma mensagem de dados assíncrona                          |    |

| Figura 4.11 – Exemplo genérico de uma mensagem de sinalização de tráfego assíncrono  |    |

| Figura 4.12 – Campos introduzidos por cada ASM                                       |    |

| Figura 4.13 - Exemplo de um EC do FTT-SE                                             | 26 |

| Figura 5.1 – Screenshot do ambiente de desenvolvimento Analog Visual DSP++           |    |

| Figura 5.2 Versão do ambiente de desenvolvimento                                     | 28 |

| Figura 5.3 - Placa de desenvolvimento BF533 EZ-KIT Lite                              | 28 |

| Figura 5.4 - Placa de expansão ADZS-USBLAN-EZEXT                                     |    |

| Figura 5.5 - Emulador ADZS-USB-ICE                                                   |    |

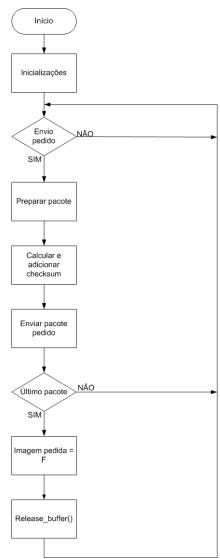

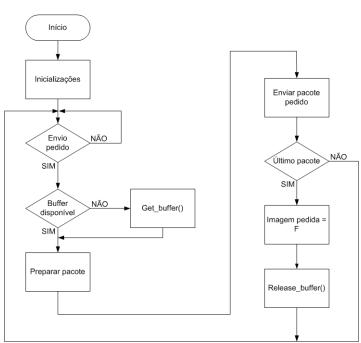

| Figura 5.6 – Algoritmo das inicializações do software para o nó slave                | 32 |

| Figura 5.7 – Algoritmo da rotina de atendimento de eventos <i>Ethernet</i>           | 33 |

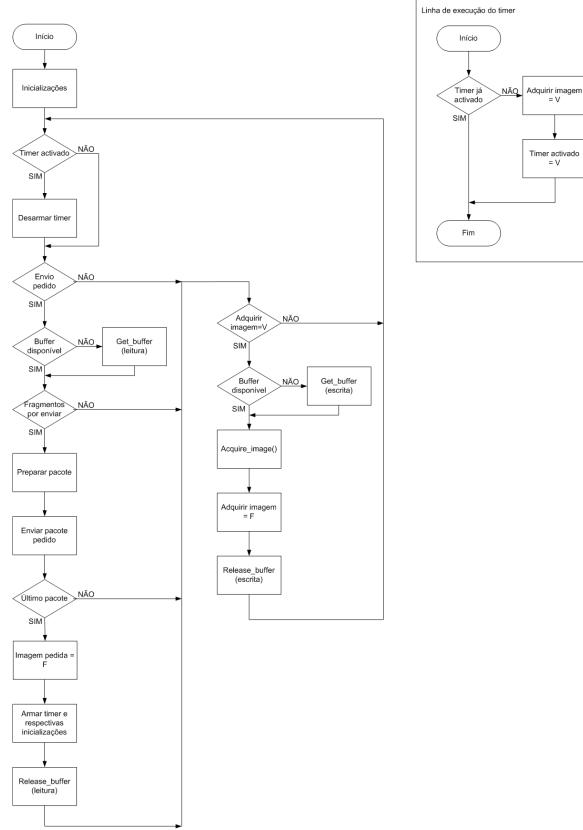

| Figura 5.8 – Algoritmo condensado da gestão de buffers                               | 36 |

| Figura 5.9 – Algoritmo da gestão de <i>buffers</i> (escrita)                         | 37 |

| Figura 5.10 - Algoritmo da gestão de <i>buffers</i> (leitura)                        | 38 |

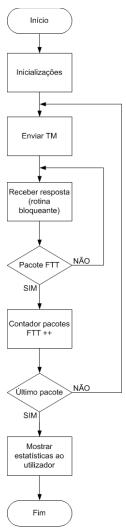

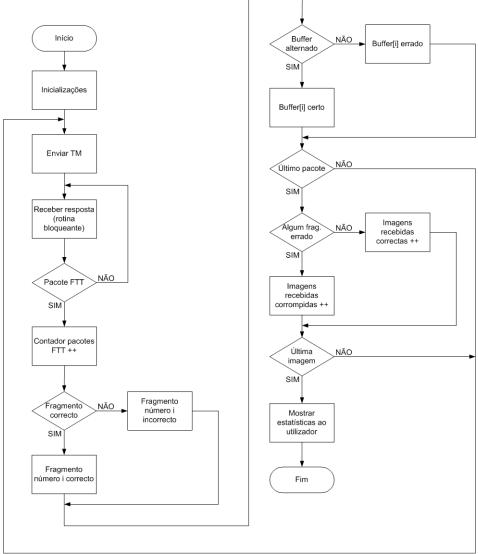

| Figura 5.11 – Diagrama de software do master para a experiência 1                    | 39 |

| Figura 5.12 – Diagrama de software do slave para a experiência 1                     | 40 |

| Figura 5.13 - Estrutura do pacote Ethernet para a experiência 2                      | 41 |

| Figura 5.14 - Diagrama de software do master para a experiência 2                    |    |

| Figura 5.15 - Diagrama de software do slave para a experiência 2                     | 43 |

| Figura 5.16 – Diagrama de software do master para a experiência 3                    | 44 |

| Figura 5.17 – Diagrama de software do slave para a experiência 3                     | 45 |

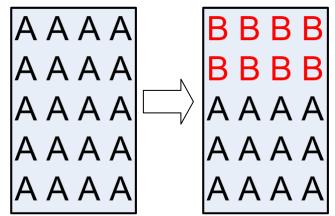

| Figura 5.18 - Exemplo do problema de um buffer sem acesso em exclusão mútua          | 46 |

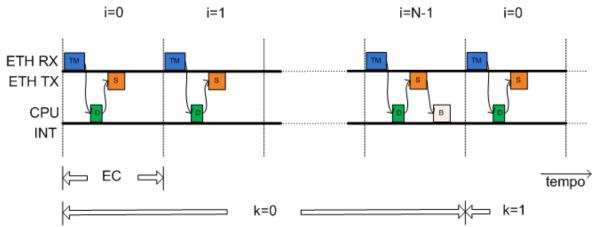

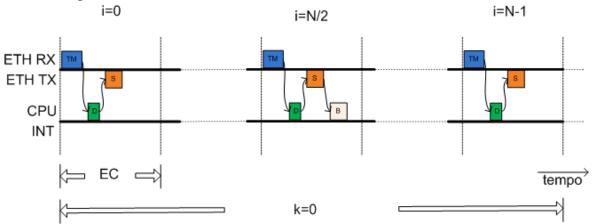

| Figura 5.19 - Diagrama temporal do teste 4: Mecanismo sequencial de troca de buffers | 47 |

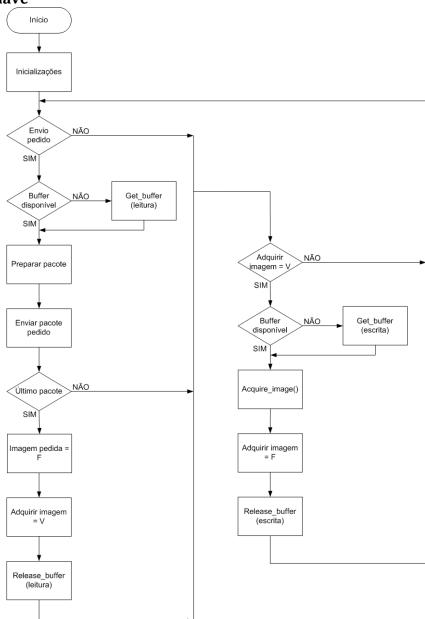

| Figura 5.20 - Diagrama de software do master para a experiência 4                    |    |

| Figura 5.21 - Diagrama de software do slave para a experiência 4                     | 49 |

| Figura 5.22 - Diagrama temporal do teste 5: Mecanismo de troca de <i>buffers</i> com |    |

| interferência em N/2                                                                 |    |

| Figura 5.23 - Diagrama de software do slave para a experiência 5                     | 51 |

| Figura 5.24 - Diagrama temporal do teste 6: Mecanismo de troca de <i>buffers</i> com |    |

| interferência de timer (1.)                                                          | 52 |

| Figura 5.25 - Diagrama temporal do teste 6: Mecanismo de troca de <i>buffers</i> com |    |

| interferência de timer (2.)                                                          | 53 |

| Figura 5.26 - Diagrama temporal do teste 6: Mecanismo de troca de <i>buffers</i> com                |    |

|-----------------------------------------------------------------------------------------------------|----|

| interferência de timer (3.)                                                                         | 54 |

| Figura 5.27 - Diagrama temporal do teste 6: Mecanismo de troca de <i>buffers</i> com                |    |

| interferência de timer (4.)                                                                         | 54 |

| Figura 5.28 - Diagrama temporal do teste 6: Mecanismo de troca de <i>buffers</i> com                |    |

| interferência de timer (5.)                                                                         | 54 |

| Figura 5.29 - Diagrama temporal do teste 6: Mecanismo de troca de <i>buffers</i> com                |    |

| interferência de timer (6.)                                                                         | 55 |

| Figura 5.30 - Diagrama temporal do teste 6: Mecanismo de troca de <i>buffers</i> com                |    |

| interferência de timer (7.)                                                                         | 55 |

| Figura 5.31 - Diagrama de software do slave para a experiência 6                                    | 56 |

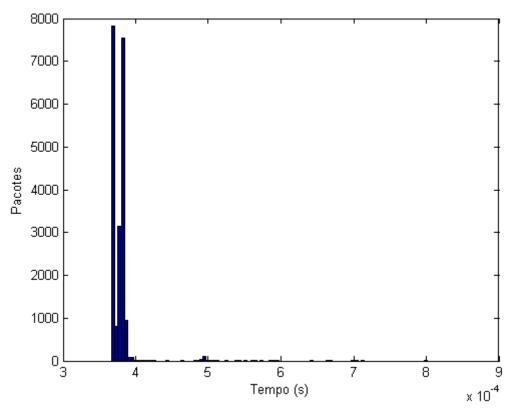

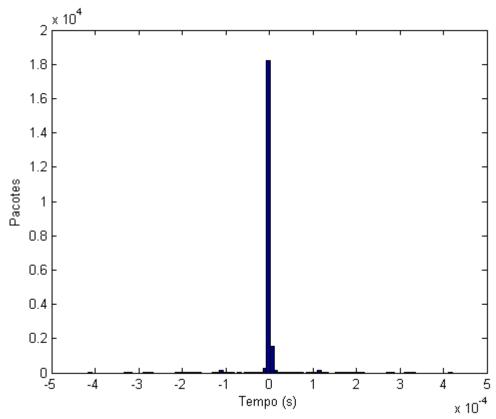

| Figura 6.1 – Latência entre a <i>Trigger Message</i> do <i>master</i> e resposta do <i>slave</i>    | 57 |

| Figura 6.2 – <i>Jitter</i> relativo entre pacotes sucessivos de resposta ao <i>master</i> (teste 1) | 58 |

# Lista de tabelas

| Tabela 6.1 - Valores de latência entre o pedido do master e a resposta do slave (experiência |

|----------------------------------------------------------------------------------------------|

| 1)58                                                                                         |

| Tabela 6.2 - Valores de latência entre o pedido do master e a resposta do slave (experiência |

| 3)59                                                                                         |

| Tabela 6.3 - Valores de latência entre o pedido do master e a resposta do slave (experiência |

| 4)59                                                                                         |

| Tabela 6.4 - Valores de latência entre o pedido do master e a resposta do slave (experiência |

| 5)60                                                                                         |

| Tabela 6.5 - Valores de latência entre o pedido do master e a resposta do slave (experiência |

| 6), varrendo um ciclo elementar                                                              |

# Lista de siglas e acrónimos

ADM - Asynchronous Data Message

ASM - Asynchronous Signaling Message

B&R - Bernecker + Rainer Industrie-Elektronik

**CAN** – Controller Area Network

**CN** – Controlled Node

CPU – Central Processing Unit CRC – Cyclic Redundancy Check

**CSMA/CD** – Carrier Sense Multiple Access/Collision Detection

EC – Elementary Cycle

**EPSG** – Ethernet POWERLINK Standardization Group

**FCS** – Frame Check Sequence

**FPGA** – Field-Programmable Gate Array

**FTT-CAN** – Flexible Time Trigger over Controller Area Network

**FTT-Ethernet** – Flexible Time Trigger over Ethernet

FTT-SE — Flexible Time Trigger over Switched Ethernet

IEEE — Institute of Electrical and Electronics Engineers

**IFG** – InterFrame Gap

**IRT** – Isochronous Real-Time

ISO – International Organization for Standardization

JTAG – Joint Test Action Group

LAN – Local Area Network

LED – Light-Emitting Diode

MN – Managing Node

NIC – Network Interface Controller

OUI – Organizationally Unique Identifier

**PDU** – Protocol Data Unit

PLC – Programmable Logic Controller

PReq - Poll Request

PRes - Poll Response

PROFIBUS - PROcess Field BUS

PROFINET - PROcess Field NET

**PROFINET CBA** – PROFINET Component Based Automation

**PROFINET IO** – PROFINET Input/Output

**QoS** – Quality of Service

RAM - Random Access Memory

RC - Rate Constrained [traffic]

RS-232 - Recommended Standard 232

RSI - Rotina de Serviço à Interrupção

**RT** – Real-time

SAE – Society of Automotive Engineers

SDM – Synchronous Data Message

SDRAM – Synchronous Dynamic Random Access Memory

SoC – Start of Cycle

**SPOF** – Single Point Of Failure

TCP/IP - Transmission Control Protocol/Internet Protocol

**TDMA** – Time Division Multiple Access

TM

Trigger MessageTime Triggered [traffic]Universal Serial BusVoice over Internet Protocol TT USB VoIP

## Capítulo 1

# 1 Enquadramento e motivação

Neste capítulo é feita inicialmente uma introdução ao tema desta dissertação, de seguida é apresentado trabalho anteriormente desenvolvido que serviu de base a este e que partilha alguns aspectos, no campo do estudo de sistemas distribuídos e sistemas de temporeal.

De seguida são apresentados os objectivos desta dissertação e no final deste capítulo é apresentada a estrutura da mesma.

### 1.1 Descrição da dissertação

Ao longo dos últimos 30 anos, têm aparecido inúmeras redes de campo (*fieldbuses*), para dar resposta a carências específicas no âmbito do controlo e automação industrial. No entanto, sofrem de algumas limitações inerentes ao facto de serem soluções particulares e inflexíveis.

Ao longo dos tempos, a tendência tem-se alterado, o mercado tem pedido respostas mais flexíveis e compatíveis. Pretende-se ainda que a solução disponibilize alguma possibilidade de evolução ao longo do tempo, que não implique uma mudança drástica quando estiver datada. Além de tudo isto, enquanto no passado as exigências de largura de banda eram muito reduzidas (pois a quantidade de informação a transmitir era diminuta), hoje em dia, com soluções de controlo baseadas por exemplo, em sistemas de visão, as necessidades de largura de banda são muito elevadas e com tendência para crescer sustentadamente.

A rede *Ethernet* aparentemente responde a todas estes pontos: é uma tecnologia bem conhecida, testada exaustivamente, livre de patentes e bastante normalizada. Oferece ainda a possibilidade de integrar uma única solução de comunicação integrada. Tomando o exemplo de uma fábrica, pode permitir a comunicação desde o controlo de automação, fazer a ponte entre o meio fabril e a parte administrativa, e por fim, responder a todas as necessidades de tecnologias de informação dessa mesma parte administrativa: interligação com a *internet*, rede interna (dados, *Voice over Internet Protocol* – VoIP, vídeo conferência), etc.

Infelizmente, a rede *Ethernet* como a conhecemos tipicamente associada à camada TCP/IP (*Transfer Control Protocol/Internet Protocol*), é incapaz de dar garantias a tráfego de tempo-real. O mecanismo CSMA/CD (*Carrier Sense Multiple Access With Collision Detection*), que existe para prevenir colisões, adiciona um grau de indeterminismo, atrasando o tráfego, e pior que isso, torna impossível de prever os instantes da sua transmissão.

Para colmatar esta limitação da rede *Ethernet*, foi criado um *standard* que evita as colisões: *switched Ethernet*. Além de evitar as colisões, maximiza ainda a largura de banda disponível. No entanto, não resolve o problema de imprevisibilidade do tráfego: em vez de haver indeterminismo ao nível das colisões, existe agora graças ao mecanismo de filas de espera do *switch*. Actualmente, devido à descida de preços dos *switches*, a versão *switched* da rede *Ethernet* substituiu quase totalmente a versão *shared*, seja em ambiente industrial, empresarial ou doméstico.

De forma a dotar a rede *Ethernet* com garantias de tempo-real, diversas entidades têm desenvolvido várias formas e tentado promover as mesmas.

A estas adaptações da rede *Ethernet*, dá-se o nome de *Industrial Ethernet*. Esta dissertação utiliza como base uma dessas adaptações, o protocolo FTT-SE (*Flexible Time Trigger over Switched Ethernet*). Um dos objectivos é o de criar uma camada de *software* que permita fazer o *interface* entre uma câmara de vídeo com porta *Ethernet* e o protocolo FTT-SE.

#### 1.1.1 Trabalho anterior

O protocolo FTT-SE [1] utilizado neste trabalho, é uma evolução do protocolo FTT-Ethernet [2], que por sua vez sofre de influências do protocolo FTT-CAN [3]. Este último trabalho visava conferir propriedades de flexibilidade e determinismo ao protocolo CAN (Controller Area Network) [4].

Em [2], foi apresentado o mesmo paradigma sobre *Ethernet* e em [1] sobre *switched Ethernet*. Na dissertação de mestrado [5], foi caso de estudo uma aplicação prática do protocolo FTT-SE.

#### 1.1.2 Objectivos

Tem-se assistido a um crescimento enorme no mercado de áreas de visão. Seja na área da indústria (controlo de processos e/ou inspecção de qualidade), na área da robótica móvel (como auxílio à navegação), no auxílio de condução (sistemas que detectam a saída do automóvel da via), ou ainda na área da militar e/ou segurança (detecção de intrusão, etc).

Existindo um grande interesse na área de visão artificial, muitas vezes com uma malha de controlo associada, controlo esse com requisitos temporais de actuação sobre o sistema, seria um tema de estudo muito interessante aplicar uma solução de visão artificial a um protocolo de tempo real, como forma de validação do mesmo.

Tem-se ainda observado a descentralização do poder de processamento nos sistemas em geral. Essa tendência deve-se a vários factores, como por exemplo a redundância, o custo, etc. Os sistemas passam de centralizados para distribuídos. Para um sistema distribuído funcionar, a comunicação entre os vários componentes é vital.

É importante então criar condições para que essa comunicação seja bem sucedida, e para isso existem protocolos de comunicação de tempo-real.

No âmbito desta dissertação, implementou-se a camada de transporte dos dados adquiridos por uma câmara com *interface Ethernet*, tendo em vista o seu futuro tratamento por um controlador. A câmara com *interface Ethernet* e respectivo suporte foram disponibilizados pela empresa Riamolde - Engenharia e Sistemas S.A. .

Os objectivos desta dissertação são os seguintes:

- Estudo de conceitos básicos sobre tempo-real e comunicações tempo-real;

- Estudo da rede Ethernet e do standard IEEE 802.1D-1998;

- Estudo do protocolo FTT-SE;

- Estudo do hardware e software das câmaras RiaVision;

- Implementação e validação da *stack* FTT-SE na câmara RiaVision;

- Implementação e validação de uma *stack* TCP/IP com gestão de *Quality of Service* (QoS) (layer 2) na câmara RiaVision;

- Avaliação das funcionalidades de gestão dinâmica de QoS do protocolo FTT-SE:

- Integração no demonstrador.

#### 1.2 Estrutura da Dissertação

Esta dissertação encontra-se dividida em sete capítulos, divididos da seguinte forma:

#### • Capítulo 1 - Enquadramento e motivação

Neste primeiro capítulo, é apresentada a motivação que levou a este trabalho, é descrito algum trabalho anterior feito neste âmbito, e por fim é descrita a estrutura desta dissertação.

# • Capítulo 2 - Conceitos Fundamentais

Este capítulo apresenta alguns conceitos fundamentais necessários para a compreensão desta dissertação.

#### • Capítulo 3 - A rede *Ethernet*

Sendo hoje em dia um *standard* importantíssimo nas comunicações, e sendo ainda a rede que esta dissertação utiliza como base de trabalho, neste capítulo a rede *Ethernet* é apresentada com maior detalhe. Inicialmente é relatada alguma história desta rede, seguidamente é apresentado o protocolo de comunicação, depois são descritas algumas formas que foram criadas para complementar a rede *Ethernet* de formas a conseguir ter garantias de tempo-real.

#### • Capítulo 4 - Flexible Time Trigger (FTT)

Este capítulo é dedicado à explicação em maior detalhe do paradigma utilizado nesta dissertação, o paradigma FTT. É descrita a sua história e evolução ao longo dos tempos, é apresentada a sua arquitectura base e o protocolo FTT-SE é apresentado em maior detalhe.

#### • Capítulo 5 - Sistema desenvolvido

Neste capítulo é apresentado em maior detalhe o sistema desenvolvido que serviu como base de trabalho desta dissertação. É apresentado o *hardware* utilizado, e o *software* existente que lhe serve de suporte. Finalmente é apresentado o *software* desenvolvido no âmbito da dissertação.

#### • Capítulo 6 - Resultados experimentais

Neste capítulo apresenta-se um conjunto de testes experimentais que foram desenvolvidos com o objectivo de verificar a correcção da implementação da camada de comunicação, bem como o respectivo desempenho temporal.

#### • Capítulo 7- Conclusões

No último capítulo desta dissertação, é feita uma análise aos resultados obtidos e objectivos alcançados, e são feitas algumas sugestões de trabalho futuro tendo em vista a continuação desta dissertação.

# Capítulo 2

### 2 Conceitos Fundamentais

Neste capítulo são introduzidos conceitos fundamentais que suportam teoricamente o trabalho desenvolvido no âmbito desta dissertação.

São introduzidos os conceitos de sistema, sistema de controlo, sistema de tempo-real, sistema centralizado *versus* distribuído.

#### 2.1 Definição de sistema

Um sistema, é um conjunto de entidades que interagem entre si ou são interdependentes, formando um todo-integrado [6].

Este conceito de todo-integrado, significa que cada componente do sistema coopera com outros à sua volta, tendo um objectivo comum.

Um exemplo de um sistema, será o de um automóvel. O volante serve para mudar de direcção, o pedal do travão para reduzir a velocidade do automóvel, etc. No entanto, todos os componentes do automóvel servem o objectivo final, de formar um meio de transporte.

Existem vários tipos de sistema, entre eles mecânicos, eléctricos, hidráulicos, económicos, etc.

#### 2.2 Definição de sistema de controlo

A um sistema que consiga gerir, comandar, dirigir ou regular outros elementos ou sistemas, define-se como sistema de controlo [7].

A teoria de sistemas de controlo visa modelar matematicamente o sistema de controlo em estudo, fazendo com que este manipule as causas, tendo em vista o efeito desejado.

#### 2.3 Evolução do controlo digital

Com a diminuição dos custos da electrónica digital, tem-se assistido à evolução de uma tendência da substituição do controlo analógico pelo controlo digital.

A disponibilidade de processadores, quer na variedade de escolha, quer na disponibilidade por parte dos fabricantes por produção em grande escala, tem sido responsável por esta evolução.

O controlo digital tem também muitas outras vantagens, entre elas:

- Baixo custo:

- Generalidade (tanto se pode controlar um processo hidráulico, como um eléctrico, por exemplo);

- Parâmetros de controlo facilmente ajustáveis (edição de software);

- Insensibilidade ao meio, garantindo fiabilidade e reprodutibilidade de resultados;

- Escalabilidade:

Com o aparecimento deste tipo de sistemas computacionais, foi necessário criar respostas para tratar de sistemas com restrições temporais.

#### 2.4 Sistema de Tempo-Real

Um sistema de tempo-real, é um sistema computacional com restrições temporais precisas em relação ao ambiente que o rodeia [8].

Como tal, o correcto comportamento do sistema deixa de ser apenas baseado nos resultados produzidos na parte de controlo, mas também nos instantes temporais em que estes ocorrem. "A reacção [de um sistema] que ocorra fora de tempo pode ser inútil ou mesmo até perigosa" [8].

Os sistemas cruciais nos quais a nossa sociedade assenta estão muitas vezes dependentes em parte, ou totalmente, de sistemas de tempo-real. Alguns exemplos incluem sistemas:

- Militares.

- Aviónicos,

- Automotivos.

#### 2.4.1 Significado

A característica base de um sistema de tempo-real é, tal como o nome indica, o tempo. O sistema depende portanto, do meio e do tempo em que as interacções ocorrem.

Além disso, a parte "real" do nome, implica que a reacção do sistema a eventos externos terá de ocorrer durante a sua evolução. Para tal acontecer, é fundamental que a escala temporal usada para medir o tempo interno do sistema, seja a mesma que é usada para medir o tempo externo do sistema, ou seja o tempo em que os eventos ocorrem.

Existe no entanto, um equívoco comum ao considerar que um sistema de temporeal é um sistema rápido. Se tal fosse verdade, todos os problemas aliados ao tempo-real, seriam resolvidos com processadores com grande poder de processamento.

Num sistema de tempo-real, é usual haver processamento paralelo, e consequentemente várias tarefas simultâneas. Assim, pode acontecer que umas tarefas bloqueiem outras, gerando atrasos imprevisíveis, não adiantando o facto de ter um processador mais rápido. É necessário que exista um escalonamento adequado.

É portanto óbvio que não interessa a um sistema de tempo-real que seja rápido, mas sim adaptado ao meio em que se insere. Espera-se que o sistema seja reactivo.

Importa também introduzir o conceito de *deadline*. Este é o tempo máximo em que uma tarefa tem de terminar a sua execução.

As tarefas podem ser classificadas segundo as consequências de perdas de deadlines:

*Hard real-time* — Tarefas em que a perda de *deadline* pode levar a uma falha catastrófica do sistema. Pode implicar perdas materiais elevadas ou perdas de vidas humanas. Em relação à utilidade do resultado do processamento fora de tempo das tarefas, este pode ser inútil ou até mesmo prejudicial.

Um exemplo de uma *deadline* perdida com consequências catastróficas: um condutor de um automóvel carregar no pedal do travão e este não é accionado. As consequências podem ser gravíssimas (danos no automóvel e/ou ocupantes do veículo, outros condutores, etc).

Um exemplo em que o resultado do processamento de uma tarefa seja prejudicial: um atraso na leitura da posição de um *flap* de um avião. A leitura terá informação errada

nesse instante, levando o sistema a agir de forma contrária ao necessário no momento, contribuindo para a perda do controlo do avião.

Firm real-time — Tarefas em que a perda de deadline leva a um comportamento problemático mas não catastrófico do sistema. Se o sistema for modelado para conseguir conviver com perdas de deadlines, pode-se tentar minimizar as suas consequências. Um exemplo, streaming de vídeo e/ou voz. No caso do incumprimento de uma deadline de um pacote, deixaria de haver imagem/ voz. A utilidade dos pacotes que chegam fora de tempo é nula, e como tal são descartados.

No entanto, é possível contornar este problema utilizando técnicas para tentar recriar os pacotes em falta a partir de anteriores.

**Soft real-time** — Tarefas em que a perda de *deadlines* causa degradação do desempenho do sistema. A utilidade dos resultados do processamento das tarefas após perda de *deadline* vai diminuindo ao longo do tempo. Por exemplo, apesar das imagens adquiridas por um *robot* através de visão artificial estarem ligeiramente atrasadas devido ao processamento de imagem, estas poderão ter alguma utilidade para tomadas de decisões em relação ao posicionamento do *robot* (desvio de obstáculos).

*Non real-time* – As tarefas que não têm restrições temporais. A utilidade dos dados gerados por estas tarefas têm sempre utilidade ao longo do tempo. São normalmente executadas num regime de *best-effort*, ou seja, se houver recursos após a execução das tarefas *hard* e *soft-real time*, então as *non real-time* serão executadas.

Tipicamente os sistemas têm tarefas *hard*, *soft* e *non real-time*, como visto no exemplo anterior. É então necessário agendar as diferentes tarefas conforme as diferentes prioridades. Neste tipo de sistema híbrido, é preciso garantir os tempos das *hard tasks*, e minimizar os tempos de resposta das *soft tasks*.

#### 2.4.2 Tipos de sistemas de tempo-real

Existem duas classificações de sistemas de tempo-real. Cada sistema é classificado conforme a sua tolerância à perda de *deadlines* por parte das suas tarefas.

#### Non real-time

Os sistemas do tipo *non real-time* são aqueles que não apresentam nenhum requisito temporal do tipo *hard, soft* ou *firm*.

#### Soft real-time

Os sistemas do tipo *soft* são aqueles que apresentam pelo menos um requisito temporal do tipo *soft* ou *firm*. No caso de incumprimento destes mesmos requisitos, o sistema pode ficar comprometido mas não de uma maneira que possa ser considerada perigosa.

#### Hard real-time

Os sistemas do tipo hard são aqueles que apresentam, pelo menos, um requisito temporal do tipo hard. No caso de incumprimento destes mesmos requisitos, o sistema

ficará comprometido de uma forma grave, e as consequências que daí advêm são perigosas e/ou catastróficas.

#### 2.4.3 Classificação do tipo de mensagens em relação à sua periodicidade

Num sistema distribuído de tempo-real, o tráfego pode ser dividido em três grupos. Estes grupos categorizam-no quanto à natureza de activação das mensagens.

Estes três grupos são:

- **Tráfego periódico** mensagens que são despoletadas com uma cadência certa, tendo como intervalo entre si um período bem definido (por ex: leitura do valor de um sensor);

- **Tráfego esporádico** mensagens que são despoletadas com um intervalo indefinido, mas com um tempo mínimo entre si (por ex: tráfego numa rede de computadores pode não haver, como haver uma rajada de mensagens, mas nunca mais do que uma num intervalo individual);

- Tráfego aperiódicas mensagens cujo padrão de activação só consegue ser caracterizado probabilisticamente (por ex: o carregar num botão por parte de um utilizador).

#### 2.5 Características de um sistema de tempo-real

Existem algumas características necessárias para se tratar de um sistema de temporeal:

- **Temporais:** As acções que o sistema pratica têm de estar correctas e no tempo certo;

- Carga máxima: As tarefas têm de ser agendadas para que não colidam temporalmente, ou seja, que não fiquem suspensas quando não era suposto. Ora para tal acontecer, o sistema deve ser projectado para quando as tarefas estão a funcionar no pico da sua actividade (*peak-load*). Tem de se garantir que o sistema está preparado para lidar com o **pior caso** (*worst-case scenario*);

- **Previsibilidade:** Para se garantir um mínimo de desempenho, o sistema tem de conhecer todas as consequências das suas decisões. Se alguma tarefa não puder ser garantida, têm de ser tomadas medidas alternativas, para que não ocorram problemas de maior;

- Tolerância a falhas: Um sistema de tempo-real é na maior parte dos casos um sistema de alta disponibilidade [9] e é sempre responsável por tarefas críticas. É um sistema que se pretende sempre funcional. Não pode o sistema falhar por causa de uma falha de um componente individual. Os componentes críticos do sistema ou SPOF [10] (Single Point Of Failure) terão então de ser tolerantes a falhas, através de redundância.

- **Fácil manutenção/Modularidade:** O sistema deve ser modular em cada componente para ser fácil a sua manutenção, quer por necessidade (avaria de um componente) ou para fácil introdução de novas funcionalidades.

#### 2.6 Sistemas de controlo centralizado versus distribuído

A forma mais simples e intuitiva, é a de controlo centralizado. Uma só entidade controla todo um sistema. Este tipo de controlo é eficaz quando existem poucas variáveis a controlar: quer pelo poder de processamento exigido, quer pela complexidade de interligação da entidade central com todas as outras.

Tomando como exemplo uma fábrica, em que existem milhares de sensores, ter um só computador central poderia ser problemático: milhares de metros de cabo, e seria preciso um super-computador, com elevado poder de processamento e com inúmeras ligações. Além de ser difícil tal acontecer, teria ainda um custo elevado.

Estes factores, conjugados com o aumento de disponibilidade de processadores de baixo custo, levou à vulgarização do conceito de arquitectura distribuída. Com a disseminação desta, surgiu a necessidade de criar uma rede comum a todos os dispositivos: surgiu assim o conceito de *fieldbus* ou rede de campo.

## Capítulo 3

## 3 A rede Ethernet

A rede *Ethernet* [11] surgiu no centro de investigação Palo Alto da Xerox, criação de Bob Metcalfe. Foi criada a 22 de Maio de 1973, a partir da necessidade de ligar um computador a uma impressora laser. Na altura conseguia disponibilizar uma largura de banda de 2.94Mbit/s.

Foi adoptada como um standard do IEEE [12], 802.3 [13-14], e tem sofrido várias evoluções ao longo dos tempos. Apresentam-se algumas normas mais relevantes:

- 802.3i-1990 10BASE-T over twisted pair

- 802.3u-1995 100Base-T Fast Ethernet and Auto-Negotiation

- 802.3x-1997 Full Duplex standard

- 802.3z-1998 1000Base-T Gigabit Ethernet over fiber-optic

- 802.3ab-1998 1000BASE-T Gbit/s Ethernet over twisted pair

- 802.3ae-2003 10 Gbit/s (1,250 MB/s) Ethernet over fiber-optic

- 802.3af-2003 Power over Ethernet (12.95 W)

- 802.3at-2009 Power over Ethernet enhancements (25.5 W)

- 802.3ba-2010 40 Gbit/s and 100 Gbit/s Ethernet

## 3.1 Breve descrição do protocolo

Inicialmente, a rede *Ethernet* apresentava uma topologia em *bus* com cabo coaxial, aparecendo posteriormente a topologia estrela, com *hubs* a permitirem a ligação de vários nós ou *Network Interface Cards* (NIC's). Porém em ambos os casos existe apenas um domínio de colisão. Para resolver colisões, o protocolo utiliza um esquema de acesso ao meio (CSMA/CD).

De uma forma simplificada, quando um NIC, pretende transmitir, actua da seguinte forma:

- Espera até que o meio esteja livre.

- Espera um determinado tempo (*interframe gap period*).

- Começa a transmissão.

- Houve colisão? Se sim, então salta para o método de colisão detectada.

- Limpa os contadores de retransmissão e termina a transmissão.

#### Caso haja uma colisão:

- Efectua a transmissão de uma sequência especial (*jam signal*), de forma a todos os NIC's detectarem a colisão.

- Incrementa o contador de retransmissão.

- Foi atingido o número máximo de tentativas de retransmissão? Se sim, é assinalado como erro de retransmissão.

- Espera um tempo pseudo-aleatório, na tentativa de não voltar a transmitir ao mesmo tempo que outro NIC.

- Recomeça o procedimento inicial de tentativa de transmissão.

O tempo pseudo-aleatório, é calculado com base no número de retransmissões, pois duplica a cada colisão detectada. Este mecanismo tem o nome de *exponential back-off*.

Após 10 colisões o valor de espera não aumenta mais (*truncated exponential back-off*). Se ao final de 16 tentativas não se conseguir transmitir a mensagem, dá-se um erro de transmissão.

Existindo por exemplo apenas dois NIC's na rede, a probabilidade de colisão é muito baixa. No entanto, à medida que uma rede cresce, a probabilidade de colisões aumenta. Ao se verificar este aumento, o desempenho da rede desce consideravelmente (thrashing). Para colmatar este problema, surgiu em 1989 na empresa Kalpana, o primeiro switch Ethernet.

O switch tem características muito vantajosas sobre os hubs:

- Cria um domínio de colisão por porta. No caso de cada porta ter ligada apenas um NIC elimina por completo as colisões.

- Contém uma tabela em que associa a cada porta o(s) NIC('s) a si ligados, possibilitando o reencaminhamento de tráfego apenas para a estação destino.

- Permite transmissões simultâneas, aumentado a largura de banda útil para cada estação.

Resolve ainda um problema do protocolo *Ethernet*, não ligado ao desempenho. A filosofia "um fala, todos ouvem", levava a que uma pessoa mal intencionada pudesse interceptar todo o tráfego da rede. Facilmente se imagina os problemas que daí poderiam advir (roubo de passwords ou outro tipo de informação privilegiada, etc).

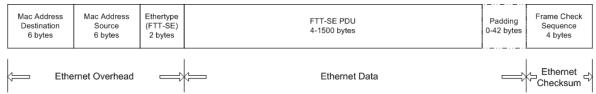

O formato da trama *Ethernet* está representado na Figura 3.1 contém os seguintes campos:

- **Preamble Field** (8 *bytes*) Contém uma sequência padrão, usada para sincronização entre estações.

- **Destination** (6 *bytes*) Endereço físico da estação-destino.

- **Source** (6 *bytes*) Endereço físico da estação-origem.

- **Data** (0-1500 *bytes*) Dados a serem enviados.

- **Padding** (0-46 *bytes*) Usado no caso em que o tamanho da trama é inferior ao tamanho mínimo imposto pelo standard usado. Para 100Base-T por exemplo, é de 46 Bytes para o campo de dados, 64Bytes total.

- **Frame Check Sequence (FCS)** (4 *bytes*) Utilizado para detecção e correcção de erros.

- **Interframe Gap** (**IFG**) (12 *bytes*) Tempo mínimo entre frames consecutivas, para facilitar a sincronização entre estações,

| Preamble + Start-of-<br>Frame-Delimiter<br>8 bytes | Mac Address<br>Destination<br>6 bytes | Mac Address<br>Source<br>6 bytes | Ethertype<br>2 bytes | Data<br>42-1496 bytes | Frame Check<br>Sequence<br>4 bytes | Interframe Gap<br>12 bytes |

|----------------------------------------------------|---------------------------------------|----------------------------------|----------------------|-----------------------|------------------------------------|----------------------------|

|----------------------------------------------------|---------------------------------------|----------------------------------|----------------------|-----------------------|------------------------------------|----------------------------|

Figura 3.1 - Formato da trama Ethernet

Cada estação é obrigada a possuir um endereço físico único. Seguindo a norma do IEEE, os 3 primeiros bytes (OUI – Organizational Unique Identifier) identificam

unicamente o fabricante da NIC, sendo a atribuição dos outros 3 *bytes* da responsabilidade do fabricante, de modo a cumprir com a unicidade de endereços.

Existem muitos protocolos que pretendem conferir características de tempo-real à rede *Ethernet*, seguidamente serão apresentados alguns dos mais importantes.

## 3.2 Protocolos *Ethernet* existentes com garantias de tempo-real

Nas últimas duas décadas, têm aparecido inúmeras redes de campo para resolver problemas específicos, apresentando uma solução personalizada para cada problema. Com uma variedade tão grande, torna-se difícil perceber qual a certa para uma determinada dificuldade, e é necessário conhecer e dominar vários protocolos. Além disso, muitas das vezes são soluções proprietárias de difícil manutenção e diagnóstico de problemas.

Além disso, com a corrente demanda por largura de banda, torna-se claro que algumas redes de campo não conseguem dar resposta a necessidades emergentes de multimédia (controlo por visão ou vigilância por exemplo) e que não têm margem para expansão futura.

A rede *Ethernet* está bem disseminada, é livre de patentes, tem tido um aumento sustentando de capacidade de largura de banda ao longo dos tempos, acompanhando as necessidades dos utilizadores. Todavia, como previamente referido, o standard *Ethernet* não permite garantias de tempo-real. No entanto existem várias iniciativas que têm como objectivo colmatar essas lacunas; a este tipo de soluções que assentam no standard *Ethernet* e que o pretendem completar de modo a dar essas mesmas garantias, dá-se o nome de *Industrial Ethernet*.

Vamos de seguida abordar alguns destes protocolos conhecidos que têm como objectivo tornar a rede *Ethernet* numa rede de tempo-real.

#### **3.2.1.1 PROFINET**

PROFINET [15] (*PROcess FIeld NET*) é o padrão de *Industrial Ethernet* da PROFIBUS & PROFINET International [16] (PI) para automação. O conceito inerente a esta tecnologia propõe uma abordagem modularizada do sistema, dando ao utilizador a possibilidade de criar sistemas complexos de uma forma estruturada e sistemática. Aborda uma série de conceitos, tais como, automação distribuída (PROFINET CBA) e dispositivos de campo descentralizados (PROFINET IO).

No que ao PROFINET CBA (Component Based Automation) diz respeito, este parte do princípio que um sistema de automação pode frequentemente ser dividido em subsistemas autónomos, permitindo assim estruturá-lo de uma forma mais clara e organizada.

Um sistema PROFINET CBA é composto por vários módulos que englobam, cada um, componentes eléctricos, mecânicos, de electrónica e *software*. A funcionalidade de um módulo é encapsulada no mesmo, podendo ser visto como uma "caixa negra" pelo sistema, dado que é acedido por uma *interface* padrão. Assim, é possível criar sistemas compostos, efectuando a interligação de vários módulos entre si. Este método apresenta ainda a vantagem de tornar os módulos altamente reutilizáveis.

A PROFINET CBA faz uso de TCP/IP e RT (*real-time communication*) apresentando ciclos de transmissão com valores desde a ordem da centena de milissegundos (TCP/IP) à dezena de milissegundos (RT), o que a torna bastante adequada para comunicações entre controladores (ex: PLC's – *Programmable Logic Controller*).

Esta característica de modularidade, que pretende responder a todas as necessidades de comunicação, é apresentada na Figura 3.1 (retirada de [17]).

Figura 3.2 – Modularidade do protocolo PROFINET

A parte PROFINET IO permite a utilização de dispositivos de campo descentralizados sobre *Ethernet*. Define o acesso a periféricos de uma forma homogénea, especificando o método de troca de dados entre controladores e dispositivos. Estes seguem uma filosofia produtor-consumidor e têm como característica a elevada velocidade na troca de dados entre si. A PROFINET IO utiliza comunicações RT (*real-time communication*) e IRT (*Isochronous Real-Time*). As comunicações RT apresentam ciclos de transmissão da ordem dos milissegundos sendo adequadas para a ligação a periféricos. As comunicações IRT apresentam ciclos de transmissão da ordem dos milissegundos, o que as torna adequadas a aplicações de controlo de movimento.

Em conjunto, PROFINET CBA e PROFINET IO, cobrem a generalidade das necessidades para aplicações no âmbito da automação de uma fábrica. É precisamente no meio industrial que o PROFINET está bastante implantado, principalmente suportado pela Siemens.

O PROFINET tem ainda a vantagem de ter evoluído do PROFIBUS, e como tal teve um enorme mercado receptivo à sua entrada.

#### 3.2.1.2 ETHERNET POWERLINK

O protocolo Ethernet POWERLINK [18-23] é um protocolo determinístico de tempo-real sobre o *standard Ethernet*. Foi inicialmente introduzido pela empresa de automação Bernecker & Rainer Industrie-Elektronik [24] (B&R) em 2001 e em 2002 foi fundado o grupo Ethernet POWERLINK Standardization Group (EPSG), que é responsável pela sua manutenção. Em 2003 foi apresentada a versão 2, que acrescenta a camada de aplicação como extensão à versão 1. Esta camada é baseada nos mecanismos definidos pelo CANopen.

Tem como principal objectivo manter a máxima compatibilidade com dispositivos *Ethernet* existentes. É uma solução implementada por software e como tal não utiliza necessariamente *hardware* proprietário.

Para evitar colisões e maximizar a utilização da largura de banda, é utilizado um esquema de *Time Division Multiple Access* [25] (TDMA), chamado neste caso de *Time Slicing*. O tempo de acesso ao barramento é dividido em POWERLINK *cycles*, e por sua vez cada um deste ciclo é divido em pequenas partes e cada nó apenas pode transmitir no tempo que lhe é reservado.

O acesso ao meio é regulado por um nó *master*, chamado de *Managing Node* (MN). Além do controlo das comunicações, está ainda encarregue de gerar o sinal de relógio para sincronização dos nós na rede. Os nós *slave* ou *Controlled Nodes* (CN) apenas transmitem quando interrogados pelo MN.

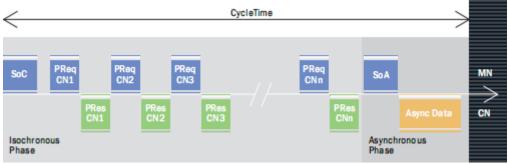

Um ciclo elementar é dividido em quatro partes, como ilustrado na Figura 3.3 (retirado de [21]):

- Start Period: Nesta fase o MN transmite uma mensagem de início de ciclo (Start Of Cycle – SoC) para todos os CN. Serve para sincronização de todos os nós.

- *Cyclic Period*: Fase isócrona em que é possível a transmissão de dados. De acordo com um escalonamento pré-configurado, os CN são convidados a transmitir os seus dados através de uma mensagem *Poll Request* (PReq). E reposta a este pedido é feita com mensagens do tipo *Poll Response* (PRes).

- Asynchronous Period: Fase em que se podem transmitir dados assíncronos sem necessidades de tempo-real.

- *Idle Period*: Tempo de inactividade do barramento até o próximo ciclo começar.

Figura 3.3 - Exemplo de um ciclo POWERLINK

Qualquer tipo de topologia pode ser usado devido à utilização de *hubs Ethernet*. Como não existe a possibilidade de colisões, o número máximo de *hubs* em cascata deixa de estar limitado a dois.

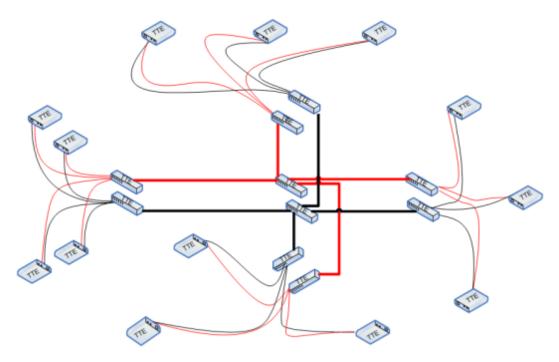

#### 3.2.1.3 TTETHERNET

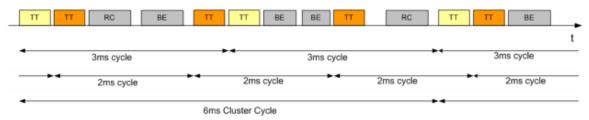

Desenvolvido pela empresa TTTech Computertechnik AG [26], o protocolo TTEthernet [27] é escalável permitindo a expansão de novos nós na rede. É ainda determinístico e tolerante a falhas. Caracteriza-se por dispor de sincronização do relógio por todos os componentes da rede, e utiliza um esquema de TDMA. Em caso de falha num dos nós, em que estes estejam a transmitir dados errados, ou o próprio nó se apercebe da falhar e suspende a sua função, ou os *switches* detectam a falha na integridade das mensagens por CRC (*Cyclic Redundancy Check*).

Existem três tipos de mensagem: *time-triggered traffic* (TT), *rate-constrained traffic* (RC) e *best-effort traffic* (BE), como se pode observar na Figura 3.4 (retirada de [27]).

A forma principal de comunicação é através de mensagens TT. Existem blocos elementares de tempo, chamados de *cluster cycle*, em que os nós podem comunicar dentro da janela temporal. Este tipo de tráfego tem precedência sobre os outros, e segundo os autores, são o tipo óptimo de mensagens para comunicação em sistemas distribuídos de tempo real. Um exemplo clássico será o tráfego gerado por um nó sensor, que se prevê que seja periódico.

Para mensagens que não têm requisitos de tempo-real tão elevados e que são menos determinísticas, existe o tipo RC. Este tipo de tráfego garante largura de banda por aplicação e que os atrasos e desvios temporais sofridos por este tipo de tráfego são bem definidos. Por exemplo, o sinal de um componente X-by-wire [28].

Por fim existe o tipo BE, que utiliza a largura de banda não utilizada pelos tipos TT ou RC, em que não existem garantias de tempo-real. Um bom exemplo deste tipo de tráfego seria o de disponibilizar o serviço de internet aos utilizadores de um avião que tem a sua rede de tempo-real baseada em TTEthernet. Evita-se assim a necessidade de utilizar duas redes para dois serviços diferentes.

Figura 3.4 - Os três tipos de tráfego TTEthernet

O protocolo é escalável, pois tanto permite uma aplicação simples com dois nós para uma aplicação de controlo industrial, como permite cobrir toda uma rede necessária, por exemplo, para um avião. A grande vantagem deste facto, é que se consegue descer os custos gerados da necessidade de mão-de-obra qualificada para trabalhar com o protocolo.

Os *switches* TTEthernet podem ser configurados como *bus-guardian*s centrais, isto é, no caso de detectarem transmissões defeituosas por parte dos nós, impedem as suas mensagens de se propagarem na rede. Permitem ainda bloquear o comportamento *babbling idiot* (quando um nó não pára de transmitir).

São suportadas todas as camadas físicas definidas no standard IEEE 802.3 para *switched networks*, e ainda *sub-networks* com diferentes larguras de banda (100Mbit/s, 1Gbit/s, ...).

É possível ainda aumentar a tolerância a falhas, adicionando múltiplos *bus* guardians redundantes, como se pode observar na Figura 3.5 (retirada de [27]).

Figura 3.5 - Rede TTEthernet com bus guardians redundantes

Existem vários produtos existentes, tanto de desenvolvimento como de aplicação. É portanto um protocolo já com aplicação real. Estão em curso à data procedimentos que têm como objectivo a estandardização em algumas organizações com importância no mundo da indústria (ISO, SAE, IEEE) com data prevista de 2012.

A empresa Honeywell foi a primeira a utilizar o protocolo TTEthernet nos seus programas de produção aeroespacial e automotivo.

Devido ao facto do trabalho desta dissertação se basear no protocolo FTT-SE, este será discutido em maior detalhe no próximo capítulo.

## Capítulo 4

## 4 Flexible Time Trigger (FTT)

Neste capítulo será apresentado com maior detalhe o protocolo *Flexible Time Trigger over Switched Ethernet* (FTT-SE), dada a importância que este tem no âmbito desta dissertação.

## 4.1 Introdução

O paradigma *Flexible Time Trigger* (FTT [2]) foi criado na Universidade de Aveiro no Laboratório de Sistemas Electrónicos, com base no protocolo FTT-CAN [3]. Na sua génese esteve o objectivo conciliar flexibilidade operacional com requisitos de tempo-real, propriedades que os protocolos existentes à altura tendiam a considerar como antagónicas. Conseguiu-se tal objectivo adoptando uma arquitectura centralizada baseada numa extensão do paradigma *master-slave*, em que o *master* concentra os requisitos de comunicação e gere o acesso ao barramento. Durante o desenvolvimento do FTT-CAN, chegou-se à conclusão que haviam conceitos fundamentais que eram possíveis de serem abstraídos da base CAN, e criar um paradigma mais generalista, denominado paradigma FTT.

Dado o crescente interesse em redes de campo utilizando *Ethernet*, foi um passo lógico tentar portar essa arquitectura para esse meio, e surgiu então o FTT-Ethernet. O problema do indeterminismo neste caso, está relacionado com o mecanismo CSMA/CD do protocolo *Ethernet*.

O protocolo sofreu várias evoluções, sendo aplicado nomeadamente a *shared Ethernet* e posteriormente a *switched Ethernet*. Esta última evolução teve um grande impacto em termos de facilidade de implementação e eficiência, pois deixou de ser necessário realizar o controlo estrito dos instantes de transmissão, devido à capacidade de serialização dos *switches Ethernet*. Houve também uma grande evolução na largura de banda disponível, devido à existência de caminhos paralelos, que permitem em certos casos a transmissão simultânea de dados.

Foram já desenvolvidos outros trabalhos como aplicação prática do trabalho teórico desenvolvido, como por exemplo na área da mecatrónica [5].

## 4.2 Breve resumo do paradigma FTT

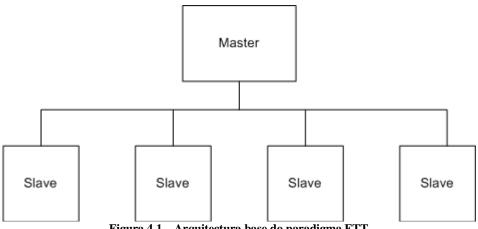

#### 4.2.1 Arquitectura base

O paradigma FTT implementa uma arquitectura produtor-distribuidor-consumidor, com um nó central, o *master*, que é responsável pelo escalonamento das mensagens. Este nó é o responsável por servir de árbitro quando os nós *slaves* tentam aceder ao barramento para comunicar.

Figura 4.1 – Arquitectura base do paradigma FTT

Essa gestão é possível através da utilização de uma unidade temporal mínima, chamada de Elementary Cycle (EC) ou ciclo elementar. Este período de tempo é a divisão mínima do acesso ao barramento.

Figura 4.2 - Ciclo elementar do paradigma FTT

Na Figura 4.2 (retirada de [2]), podem-se observar representados dois ECs com os seus diversos componentes:

#### Trigger Message (TM)

Esta mensagem é enviada pelo *master* para o barramento, e além de permitir a sincronização entre todos os nós da rede (pois marca o início do EC), indica também que mensagens poderão ser enviadas nesse EC.

#### Synchronous Window (Janela Síncrona)

Intervalo de tempo em que é possível enviar mensagens síncronas (periódicas) que tenham sido escalonadas pelo master.

## Asynchronous Window (Janela Assíncrona)

Intervalo de tempo em que é possível enviar mensagens assíncronas (aperiódicas) que tenham sido escalonadas pelo *master*.

## *Idle Time* (Tempo de inactividade)

Tempo de inactividade do barramento necessário para garantir o início atempado do EC seguinte. Note-se que pode dever-se a não existirem de facto mensagens prontas ou a o fim do ciclo estar próximo e então a transmissão de uma eventual mensagem poder exceder o tempo de ciclo restante (EC overrun).

#### 4.2.2 **Funcionalidades**

O paradigma FTT prevê que o escalonamento das mensagens seja efectuado de uma forma central pelo *master*, sendo assim possível alterar facilmente o escalonamento a ser utilizado, e que posteriormente é disseminado pela TM. Graças a esta característica, o protocolo suporta admissão e remoção online de streams de mensagens, com garantias temporais e maximização da largura de banda disponível. Além disso o algoritmo de escalonamento é uma entidade de software residente no master, logo podem ser implementados algoritmos de escalonamento arbitrários e independentes do protocolo base. Finalmente, o FTT suporta quer tráfego síncrono (i.e., activado pela passagem do tempo) quer assíncrono (i.e., activado por um evento externo). Deste conjunto de propriedades advém o adjectivo *flexible* do nome do protocolo. De uma forma mais concisa, o protocolo FTT-SE exibe as seguintes funcionalidades [2]:

- Comunicação *time-triggered* com flexibilidade operacional;

- Suporte para alterações dinâmicas tanto no conjunto de mensagens, como no escalonamento das mesmas;

- Controlo de admissão *online* para garantir a pontualidade do tráfego temporeal:

- Indicação da exactidão temporal das mensagens tempo-real;

- Suporte de diferentes tipos de tráfego: *event-triggered*, *time-triggered*, *hard real-time*, *soft real-time* e *non real-time*;

- Isolamento temporal: os diferentes tipos de tráfego não devem interferir entre si;

- Uso eficiente da largura de banda;

- Suporte eficiente de mensagens *multicast*.

## 4.3 Flexible Time Trigger over Switched Ethernet (FTT-SE)

Nesta secção é apresentada a evolução natural do FTT-Ethernet: o protocolo FTT-SE.

#### 4.3.1 Trama FTT-SE

A trama FTT-SE (Figura 4.3) é uma trama específica baseada na trama *Ethernet*. Contém os seguintes campos:

- MAC (*Media Access Control*) Address Destination (6 *bytes*): Endereço físico do nó destino.

- MAC Address Source (6 bytes): Endereço físico do nó origem.

- Ethertype (2 *bytes*): campo identificador do protocolo. No caso do protocolo FTT-SE tem o valor 0x8FF0.

- FTT-SE PDU (Protocol Data Unit) (4 a 1500 *bytes*): Campo de dados (de configuração ou no sentido estrito).

- Padding (0 a 42 *bytes*): Campo utilizado no caso de a mensagem ter menos que 64 *bytes*.

Figura 4.3 - Trama FTT-SE

## 4.3.1.1 Tipos de mensagens

Nesta secção serão apresentados os tipos de mensagens que são possíveis de serem transmitidos pelo protocolo FTT-SE:

- **1.** Trigger Message

- **2.** Mensagem síncrona de dados (*synchronous data message* SDM)

- **3.** Mensagem assíncrona de dados (*asynchronous data message* ADM)

- **4.** Mensagem assíncrona de sinalização (*asynchronous signaling message* ASM)

- **5.** Mensagem de inactividade (*Idle*)

Apenas duas ressalvas em relação à representação das tramas que serão apresentadas seguidamente:

- **1.** Todas as mensagens são encapsuladas em tramas *Ethernet*, sendo precedidas do cabeçalho *Ethernet* e terminadas pelo FCS e IFG.

- **2.** Na eventualidade da trama *Ethernet* ser menor que o tamanho mínimo de 64 *bytes*, está implícita a necessidade de *padding*.

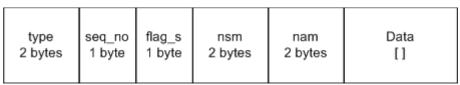

### 4.3.1.2 Trigger Message

A Figura 4.4 apresenta a estrutura base de uma *trigger message*. Esta contém os seguintes campos:

- **type** (2 *bytes*): tipo de mensagem. Neste caso, como se trata de uma *trigger message*, contem o valor **FTT\_MST\_MSG**.

- **seq\_no** (1 *byte*): número de sequência da *trigger message* enviada. Serve para que os nós consigam detectar se perderam alguma *trigger* message.

- **flag\_s** (1 *byte*): campo reservado para *flags* de controlo.

- **nsm** (2 *bytes*): número de pedidos de mensagens síncronas contidas no campo de dados.

- **nam** (2 *bytes*): número de pedidos de mensagens assíncronas contidas no campo de dados.

- data (até 1492 bytes ou limitação do protocolo): dados propriamente ditos da trigger message. Aqui serão inseridos N campos, tantos quantos referenciados por nsm e nam. Na Figura 4.4 podem-se observar os campo inseridos por cada nsm, e na Figura 4.5 estão representados os campos introduzidos por cada nam.

Figura 4.4 - Estrutura de uma trigger message

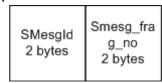

Na Figura 4.5 apresentam-se os campos inseridos na *trigger message* necessários para efectuar um pedido de transmissão de uma mensagem síncrona por parte de um *slave*. São eles:

- **SMesgId** (2 *bytes*): identificador lógico e único de mensagem a ser transmitida, sendo o seu escalonamento efectuado pelo *master*.

- **Smesg\_frag\_no** (2 *bytes*): o FTT-SE suporta fragmentação de mensagens. Este campo identifica qual o fragmento a ser enviado.

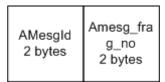

De igual forma, existe um mecanismo análogo para a gestão de mensagens assíncronas (Figura 4.6). Note-se que o formato é semelhante. A diferença entre mensagens síncronas e assíncronas prende-se essencialmente com a sua activação. As primeiras são escalonadas autonomamente pelo *master*, de acordo com a passagem do tempo, enquanto as segundas

são escalonadas também pelo *master* mas na sequência de um pedido explícito, geralmente decorrente de um evento externo.

Figura 4.5 – Campos introduzidos por cada mensagem síncrona de dados

Figura 4.6 - Campos introduzidos por cada mensagem assíncrona de dados

Na Figura 4.7, é apresentada de uma forma genérica a formação de uma *trigger message*. Na Figura 4.8, é apresentado um exemplo específico.

Figura 4.7 - Exemplo genérico de uma trigger message

#### Exemplo:

Os campos **nsm** e **nam** contem os valores 2 e 1 respectivamente. Então a *trigger message* gerada conteria dois pedidos de mensagens síncronas e um pedido de mensagem assíncrona.

Figura 4.8 - Exemplo específico da formação de uma trigger message

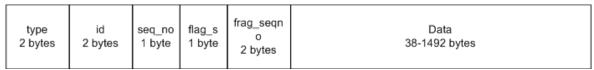

#### 4.3.1.3 Synchronous Data Message – SDM

Quando existe a necessidade de envio de dados de uma forma periódica (por exemplo, a temperatura de um sensor), estes dados são modelados como tráfego síncrono, e como tal, é utilizada esta trama para o seu envio.

A trama SDM (Figura 4.9) contém os seguintes campos:

- **type** (2 *bytes*): tipo de mensagem. Neste caso, como se trata de uma mensagem de dados síncrona, contem o valor **FTT\_SDATA\_MSG**.

- **id** (2 *bytes*): identificador lógico e único da mensagem.

- **seq\_no** (1 *byte*): número de sequência da SDM a enviar. Serve para detectar eventuais perdas de mensagens.

- **flag\_s** (1 *byte*): campo reservado para *flags* de controlo.

- **frag\_seqno** (2 *bytes*): número identificador do fragmento a ser enviado pela estação visada.

- **data** (até 1492 *bytes*): dados propriamente ditos que são possíveis de serem transmitidos.

| type<br>2 bytes | id<br>2 bytes | seq_no<br>1 byte | flag_s<br>1 byte | frag_seqn<br>o<br>2 bytes | Data<br>38-1492 bytes |

|-----------------|---------------|------------------|------------------|---------------------------|-----------------------|

|-----------------|---------------|------------------|------------------|---------------------------|-----------------------|

Figura 4.9 - Estrutura de uma mensagem de dados síncrona

#### 4.3.1.4 Asynchronous Data Message - ADM

Quando existe a necessidade de envio de dados de uma forma aperiódica ou esporádica (por exemplo, um alarme ou a pressão de um botão de um utilizador), estes dados são modelados como tráfego assíncrono, e como tal, é utilizada esta trama para o seu envio

A trama ADM (Figura 4.10) contém os seguintes campos:

- **type** (2 *bytes*): tipo de mensagem. Neste caso, como se trata de uma mensagem de dados síncrona, contem o valor **FTT\_ADATA\_MSG**.

- id (2 bytes): identificador lógico e único da mensagem a ser transmitida.

- **seq\_no** (2 *bytes*): número de sequência da mensagem ADM enviar. Serve para detectar eventuais perdas de mensagens.

- **flag\_s** (1 *byte*): campo reservado para *flags* de controlo.

- **frag\_seqno** (2 *bytes*): número identificador do fragmento a ser enviado pela estação visada.

- **data** (até 1492 *bytes*): dados propriamente ditos que são possíveis de serem transmitidos.

Figura 4.10 – Estrutura de uma mensagem de dados assíncrona

## 4.3.1.5 Asynchronous Signalling Message – ASM

Tal como anteriormente referido, na eventualidade de existirem dados assíncronos a serem enviados é necessário notificar o *master* para que este as inclua no escalonamento. As ASM servem para este propósito, reportando periodicamente ao *master* o estado interno das filas dos diversos nós.

A trama ASM (Figura 4.11) contém os seguintes campos:

- **enum** (2 *bytes*): tipo de mensagem. Neste caso, como se trata de uma mensagem de sinalização de dados assíncrona, contem o valor **FTT\_ASTATUS\_MSG**.

- **id** (2 *bytes*): identificador lógico e único do nó.

- **seq\_no** (2 *bytes*): número de sequência da ASM.

- **flag\_s** (1 *byte*): campo reservado para *flags* de controlo.

- **nam** (2 *bytes*): número de pedidos de mensagens assíncronas contidas no campo de dados.

- data (até 1494 *bytes*): estado de cada uma das filas de mensagens assíncronas.

|  | _no flag_s nam<br>yte 1 byte 2 bytes | Asynch Msg Queue Idx 1<br>4 bytes | () | Asynch Msg Queue Idx N<br>4 bytes |

|--|--------------------------------------|-----------------------------------|----|-----------------------------------|

|--|--------------------------------------|-----------------------------------|----|-----------------------------------|

Figura 4.11 – Exemplo genérico de uma mensagem de sinalização de tráfego assíncrono

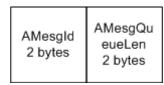

De uma forma semelhante com o que acontece com a TM, o tamanho da trama ASM é de tamanho variável, sendo função do número contido em **nam**.

O conjunto de campos apresentado na Figura 4.12, é acrescentado no campo de dados por cada mensagem aperiódica que se pretende transmitir.

Figura 4.12 – Campos introduzidos por cada ASM

Imaginando um exemplo em que seja preciso enviar uma mensagem assíncrona (por exemplo um alarme e respectiva hora), a trama seria constituída da seguinte forma:

- o campo **nam** conteria o valor 1, pois era necessário enviar uma mensagem;

- o campo **AMesgId** conteria o valor do identificador lógico da mensagem a transmitir;

- o campo **AMesgQueueLen** conteria o valor 1, pois era necessário escalonar o envio de 1 mensagem.

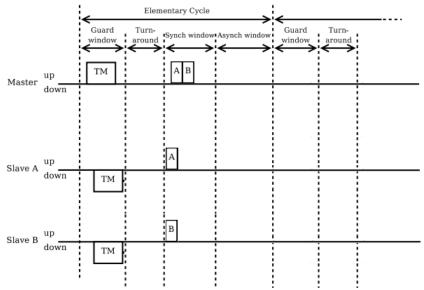

## 4.3.2 Elementary cycle do protocolo FTT-SE

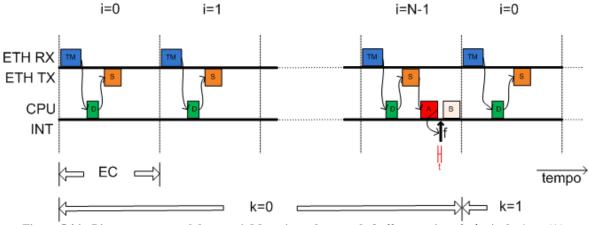

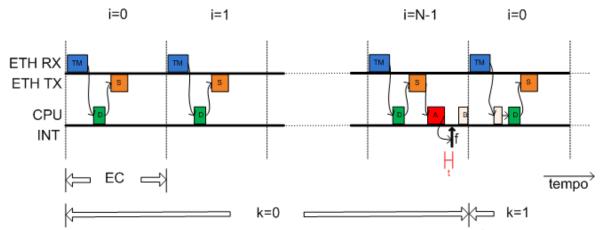

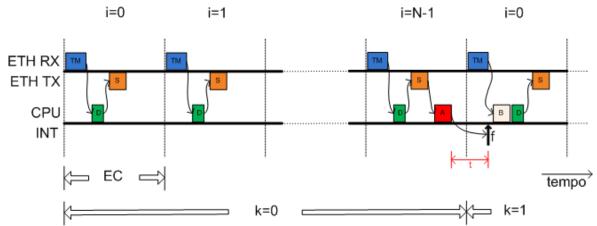

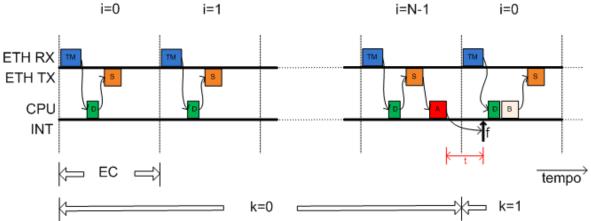

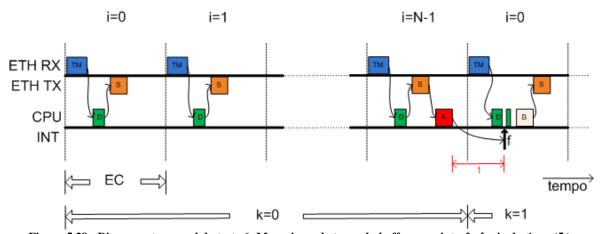

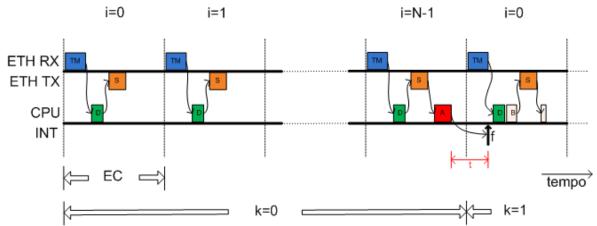

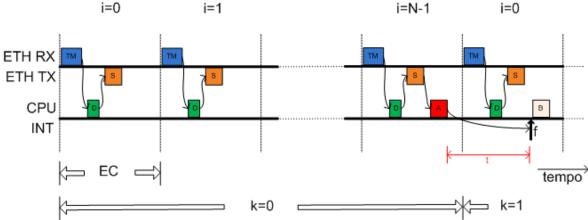

Foi já apresentado no início deste capítulo o EC do FTT-Ethernet. O meio partilhado era único, a rede *Ethernet*. Com a introdução de *switches*, passa a ser possível vários nós comunicarem ao mesmo tempo. A Figura 4.13 (adaptada de [1]) ilustra exactamente isso: vários nós a comunicarem simultaneamente.

A Figura 4.13 mostra ainda a existência de quatro sub-divisões temporais do EC:

- **1. Guard Window:** Período em que o *master* transmite as TM's para os nós que deverão transmitir informação nesse EC.

- 2. *Turn-around:* Tempo de resposta, valor configurável. Deve-se ter algum cuidado com este valor. Se for um valor muito alto, resta pouco tempo para transmitir informação, se for um valor muito baixo, alguns nós com pior desempenho podem não conseguir responder a tempo. Tipicamente é um valor configurado com o tempo de resposta do pior nó da rede.

- 3. Synch Window: Janela de tempo em que se pode transmitir tráfego síncrono/periódico.

- 4. Assynch Window: Janela de tempo em que se pode transmitir tráfego assíncrono (aperiódico ou esporádico).

Os valores da janela síncrona e da janela assíncrona, não são valores fixos, maximizando assim o aproveitamento da largura de banda.

Figura 4.13 - Exemplo de um EC do FTT-SE

## 4.4 Variantes do paradigma FTT

As secções anteriores incidiram especificamente sobre o protocolo FTT-SE. Há todavia outras implementações do paradigma FTT sobre tecnologia *Ethernet*. Foi dada ênfase ao FTT-SE devido ao facto de ter sido esta a variante específica sobre a qual o trabalho reportado nesta dissertação incidiu. Para efeitos de complementar a informação sobre esta família de protocolos, referem-se de seguida as outras duas implementações existentes, bem como as suas principais diferenças em relação ao FTT-SE.

A primeira implementação do paradigma FTT foi efectuada sobre *shared Ethernet* (FTT-Ethernet) [2]. Esta implementação tem algumas diferenças em relação ao FTT-SE na parte que respeita ao mecanismo de controlo de acesso ao meio. Enquanto no FTT-SE os nós podem transmitir as mensagens concorrentemente, pois o *switch* efectua a sua serialização, no FTT-Ethernet é necessário disparar as transmissões das mensagens em instantes diferentes, a fim de evitar colisões. Assim, a TM é ligeiramente modificada, de forma a incluir informação temporal de disparo. Adicionalmente, trata-se de um meio *broadcast* e *half-duplex*, logo a caracterização das mensagens é distinta (e.g. não é necessário indicar os portos a que os nós se ligam).

Mais recentemente foi desenvolvido o FTT-Enabled switch. Trata-se de um switch Ethernet modificado, implementado em tecnologia FPGA (Field-Programmable Gate Array). A principal diferença em termos da operação do protocolo é que deixou de ser necessário notificar o master da existência de mensagens assíncronas. Os nós enviam as mensagens assíncronas em instantes arbitrários. Quando chegam ao switch, este coloca-as numa fila e notifica internamente o master, para que este as possa incluir no escalonamento. Adicionalmente o switch traz benefícios importantes em termos de tolerância a falhas, pois pode efectuar verificações sobre as mensagens que chegam e, caso detecte anomalias (e.g. um nó com comportamento do tipo babbling idiot), pode bloquear o respectivo tráfego.

## Capítulo 5

## 5 Sistema desenvolvido

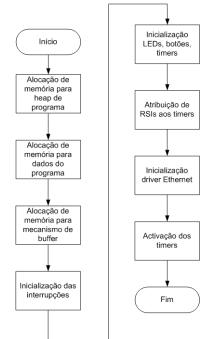

Neste capítulo são apresentados os componentes do sistema criado. Numa primeira fase é apresentado o ambiente de desenvolvimento utilizado, de seguida o *hardware* usado, depois o *software* que serviu de base ao sistema, e finalmente o *software* desenvolvido no âmbito da dissertação.

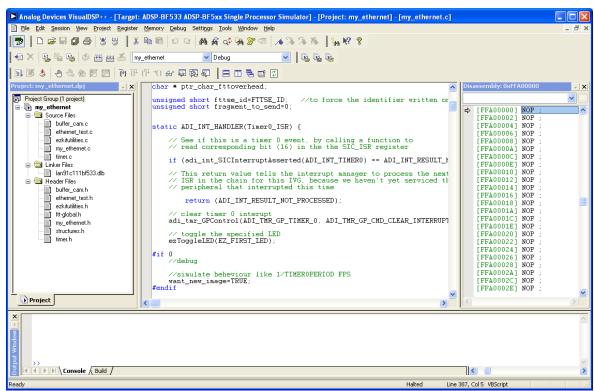

#### 5.1 Ambiente de desenvolvimento

O ambiente de desenvolvimento utilizado foi o fornecido pela empresa Analog Devices [29], a mesma empresa que fabrica o *hardware* que será descrito de seguida. Foi utilizada a versão 5.0.7.0 (Update 7) do programa Visual DSP++.

A Figura 5.1 apresenta um *screenshot* do ambiente de desenvolvimento utilizado e a Figura 5.2 apresenta a versão desse mesmo ambiente de desenvolvimento.

Figura 5.1 - Screenshot do ambiente de desenvolvimento Analog Visual DSP++

O ambiente de desenvolvimento Visual DSP++ tem as seguintes características:

- Suporta programação em linguagem C e assembly.

- Inclui diversas bibliotecas de código, entre elas *software* que permite inicializar/interagir com a *interface Ethernet*, *drivers* de baixo nível para botões, LEDs, *timers*, etc

- No que à facilidade de *debug* diz respeito, a ferramenta permite o *debug* passo-a-passo, e análise do conteúdo da memória de dados e de programa.

Figura 5.2 Versão do ambiente de desenvolvimento

## 5.2 Breve descrição do hardware

O *hardware* utilizado pode ser dividido em três partes: a placa de desenvolvimento propriamente dita, uma placa de expansão (que permite adicionar uma porta *Ethernet* e uma porta USB – *Universal Serial Bus*), e o emulador.